高位合成(HLS)と高位検証

次のRTLプロジェクトが期日に間に合うか不安になることはありませんか?期待の新設計で要求性能を満たすことができましたか?消費電力(パワー)は増えすぎていませんか?RTLが機能的に正しく、最適な構成になっていることを確認する方法はありますか。Catapult 高位合成・検証ソリューションを活用すると、こうした問題を一挙に解決できます。

設計者を強力に支援するプラットフォーム

Catapult高位合成・検証の概要

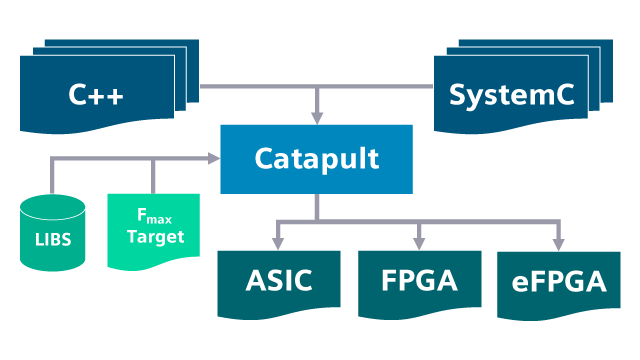

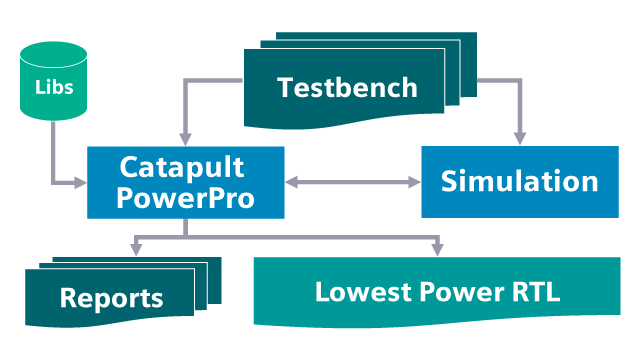

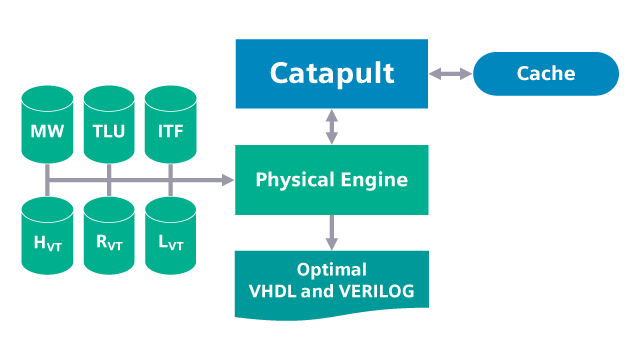

Catapultは、業界をリードするC++/SystemC高位合成ソリューションで、パワーの推定や最適化機能も有しています。さらに高位のデザインチェッカーやコード/機能カバレッジ検証だけでなく、フォーマル検証技術も広く取り入れることで、単なるCからRTLへの高位合成の枠を超えたプラットフォームと言えます。

トレンドとテクノロジ

RTLの設計と検証には時間とコストがかかりすぎる

RTLによる開発の生産性は、特に新規開発や複雑な高付加価値のブロックにおいて、著しく停滞しています。ワイヤレス、5G、AI/機械学習(ML)、ビデオ/画像処理などの分野で、優位性の確保を革新的なチップ・アーキテクチャで実現することは、RTL設計チームにとって容易なことではありません。

アーキテクチャ検討

ハードウェアがシステム性能のボトルネックになっていませんか?最適なメモリ・アーキテクチャが構成されていますか?システムとしての統合やテストの段階になってはじめて、実性能が要求を満たしていないと気づくことはないですか。

まだRTLでデバッグしているのですか?

RTL設計でのバグ発見の遅れは、市場投入機会の損失、シリコン競争力の低下、テープアウトの遅延、ECOリスクなどに直結する問題です。高位合成を用いた高位設計・検証は、サーバーやツールの開発コストを削減しながら、最初の設計から適切なRTLを実現します。

最適なパワー、性能と面積

顧客のニーズに合致したパワー、性能、面積(PPA)の最適バランスの達成は、容易なことではありません。性能が低すぎても、パワーが大きすぎても、面積が大きすぎても、製品サイクルに間に合わない可能性があります。高位合成は、高品質で高バランスな設計を早く実現できます。

Catapult高位合成(HLS)ソリューション

シーメンスのCatapult高位合成ソリューションは、C++/SystemC両言語対応、FPGA/ASIC非依存、ASICパワー推定/最適化に加えて、フィジカルを考慮した(Physical Aware)最新のマルチVth制約下での面積/性能最適化を提供します。

Catapult高位検証ソリューション

高位検証フローを加速するために必要なすべての要素を提供します。デザインチェック、コード/機能カバレッジ検証に加え、フォーマル検証を活用し、検証の時間とコストを最大80%まで削減します。

関連情報ライブラリ

Catapult 高位合成

Catapult高位合成プラットフォームの活用事例をまとめたリソース・ライブラリです。ディープ・ラーニング、コンピュータ・ビジョン、通信や動画処理などについての手法や事例を紹介しています。シーメンスEDAの高位合成・検証(HLS & HLV)は、お客様が必要とする競争力を提供します。